# MOTOR BRIDGE CONTROLLER

## 1 FEATURES

- OPERATING SUPPLY VOLTAGE 8V TO 28V, OVERVOLTAGE MAX. 40V

- OPERATING SUPPLY VOLTAGE 6V WITH IMPLEMENTED STEPUP CONVERTER

- QUIESCENT CURRENT IN STANDBY MODE LESS THAN 50µA

- ISO 9141 COMPATIBLE INTERFACE

- CHARGE PUMP FOR DRIVING A POWER MOS AS REVERSE BATTERY PROTECTION

- PWM OPERATION FREQUENCY UP TO 30KHZ

- PROGRAMMABLE CROSS CONDUCTION PROTECTION TIME

- OVERVOLTAGE, UNDERVOLTAGE, SHORT CIRCUIT AND THERMAL PROTECTION

- REAL TIME DIAGNOSTIC

Figure 1. Package

Table 1. Order Codes

| Part Number | Package     |

|-------------|-------------|

| L9904       | SO20        |

| L9904TR     | Tape & Reel |

#### 2 DESCRIPTION

Control circuit for power MOS bridge driver in automotive applications with ISO 9141bus interface.

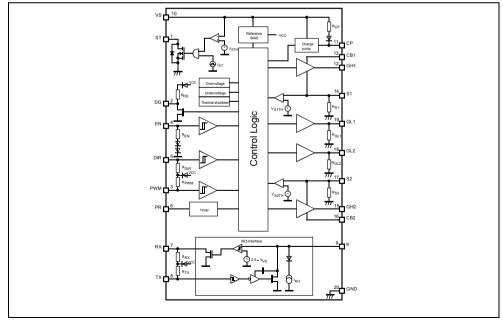

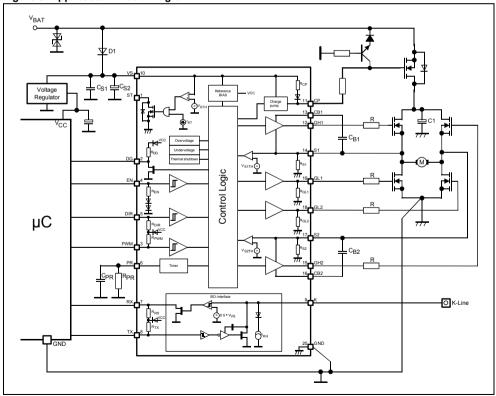

# Figure 2. Block Diagram

REV. 5

**Table 2. Pin Function**

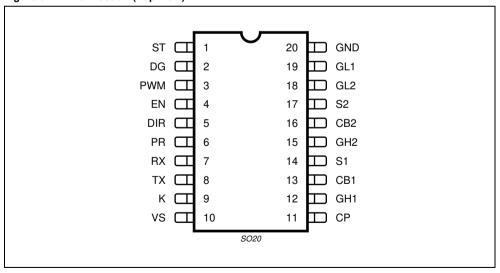

| N° | Pin | Description                                                       |

|----|-----|-------------------------------------------------------------------|

| 1  | ST  | Open Drain Switch for Stepup converter                            |

| 2  | DG  | Open drain diagnostic output                                      |

| 3  | PWM | PWM input for H-bridge control                                    |

| 4  | EN  | Enable input                                                      |

| 5  | DIR | Direction select input for H-bridge control                       |

| 6  | PR  | Programmable cross conduction protection time                     |

| 7  | RX  | ISO 9141 interface, receiver output                               |

| 8  | TX  | ISO 9141 interface, transmitter input                             |

| 9  | K   | ISO 9141 Interface, bidirectional communication K-line            |

| 10 | VS  | Supply voltage                                                    |

| 11 | CP  | Charge pump for driving a power MOS as reverse battery protection |

| 12 | GH1 | Gate driver for power MOS highside switch in halfbridge 1         |

| 13 | CB1 | External bootstrap capacitor                                      |

| 14 | S1  | Source/drain of halfbridge 1                                      |

| 15 | GH2 | Gate driver for power MOS highside switch in halfbridge 2         |

| 16 | CB2 | External bootstrap capacitor                                      |

| 17 | S2  | Source/drain of halfbridge 2                                      |

| 18 | GL2 | Gate driver for power MOS lowside switch in halfbridge 2          |

| 19 | GL1 | Gate driver for power MOS lowside switch in halfbridge 1          |

| 20 | GND | Ground                                                            |

Figure 3. Pin Connection (Top view)

**Table 3. Absolute Maximum Ratings**

| Symbol                                                               | Parameter                        | Value                        | Unit |

|----------------------------------------------------------------------|----------------------------------|------------------------------|------|

| V <sub>CB1</sub> , V <sub>CB2</sub>                                  | Bootstrap voltage                | -0.3 to 40                   | V    |

| I <sub>CB1</sub> , I <sub>CB2</sub>                                  | Bootstrap current                | -100                         | mA   |

| V <sub>CP</sub>                                                      | Charge pump voltage              | -0.3 to 40                   | V    |

| I <sub>CP</sub>                                                      | Charge pump current              | -1                           | mA   |

| $V_{DIR}$ , $V_{EN}$ , $V_{PWM}$ , $V_{TX}$                          | Logic input voltage              | -0.3 to 7                    | V    |

| I <sub>DIR</sub> ,I <sub>EN</sub> ,I <sub>PWM</sub> ,I <sub>TX</sub> | Logic input current              | ±1                           | mA   |

| V <sub>DG</sub> ,V <sub>RX</sub>                                     | Logic output voltage             | -0.3 to 7                    | V    |

| I <sub>DG</sub> ,I <sub>RX</sub>                                     | Logic output current             | -1                           | mA   |

| V <sub>GH1</sub> , V <sub>GH2</sub>                                  | Gate driver voltage              | -0.3 to V <sub>SX</sub> + 10 | V    |

| I <sub>GH1</sub> , I <sub>GH2</sub>                                  | Gate driver current              | -1                           | mA   |

| $V_{GL1}$ , $V_{GL2}$                                                | Gate driver voltage              | -0.3 to 10                   | V    |

| I <sub>GL1</sub> , I <sub>GL2</sub>                                  | Gate driver current              | -10                          | mA   |

| Vĸ                                                                   | K-line voltage                   | -20 to V <sub>S</sub>        | V    |

| V <sub>PR</sub>                                                      | Programming input voltage        | -0.3 to 7                    | V    |

| I <sub>PR</sub>                                                      | Programming input current        | -1                           | mA   |

| V <sub>S1</sub> , V <sub>S2</sub>                                    | Source/drain voltage             | -2 to V <sub>VS</sub> + 2    | V    |

| I <sub>S1</sub> , I <sub>S2</sub>                                    | Source/drain current             | -10                          | mA   |

| V <sub>ST</sub>                                                      | Output voltage                   | -0.3 to 40                   | V    |

| I <sub>ST</sub>                                                      | Step up output current           | -1                           | mA   |

| V <sub>VSDC</sub>                                                    | DC supply voltage                | -0.3 to 28                   | V    |

| V <sub>VSP</sub>                                                     | Pulse supply voltage (T < 500ms) | 40                           | V    |

| I <sub>VS</sub>                                                      | DC supply current                | -100                         | mA   |

For externally applied voltages or currents exceeding these limits damage of the device may occur!

All pins of the IC are protected against ESD. The verification is performed according to MIL883C, human body model with R=1.5k $\Omega$ , C=100pF and discharge voltage ±2kV, corresponding to a maximum discharge energy of 0.2mJ.

Table 4. Thermal Data

| Symbol                | Parameter                                       | Value      | Unit |

|-----------------------|-------------------------------------------------|------------|------|

| TJ                    | Operating junction temperature                  | -40 to 150 | °C   |

| T <sub>JSD</sub>      | Junction temperature thermal shutdown threshold | min 150    | °C   |

| T <sub>JSDH</sub>     | Junction thermal shutdown hysteresis            | typ 15     | °C   |

| R <sub>th j-amb</sub> | Thermal resistance junction to ambient 1)       | 85         | °C/W |

<sup>1.</sup> see application note 110 for SO packages.

# **Table 5. Electrical Characteristcs**

(8V <  $V_{VS}$  < 20V,  $V_{EN}$  = HIGH, -40°C  $\leq$   $T_{J}$   $\leq$  150°C, unless otherwise specified. The voltages are referred to GND and currents are assumed positive, when current flows into the pin

| Symbol                                 | Parameter                                                      | Test Condition                                                                                                                                                             | Min. | Тур. | Max. | Unit |

|----------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Supply (\                              | /S)                                                            |                                                                                                                                                                            |      |      |      |      |

| V <sub>VS OVH</sub>                    | Overvoltage disable HIGH threshold                             |                                                                                                                                                                            | 28   | 33   | 36   | V    |

| V <sub>VS OVh</sub>                    | Overvoltage threshold hysteresis <sup>2)</sup>                 |                                                                                                                                                                            |      | 1.6  |      | V    |

| V <sub>VS UVH</sub>                    | Undervoltage disable HIGH threshold                            |                                                                                                                                                                            | 6    |      | 7    | ٧    |

| V <sub>VS UVh</sub>                    | Undervoltage threshold hysteresis <sup>2)</sup>                |                                                                                                                                                                            |      | 0.66 |      | V    |

| I <sub>VSL</sub>                       | Supply current                                                 | V <sub>EN</sub> = 0 ; V <sub>VS</sub> = 13.5V; T <sub>J</sub> < 85°C                                                                                                       |      |      | 50   | μΑ   |

| lvsh                                   | Supply current, pwm-mode                                       | $V_{VS}$ = 13.5V; $V_{EN}$ = HIGH; $V_{DIR}$ = LOW; S1 = S2 = GND $f_{PWM}$ = 20kHz; $C_{CBX}$ = 0.1 $\mu$ F; $C_{GLX}$ = 4.7nF; $C_{GHX}$ = 4.7nF; $C_{PR}$ = 150 $\mu$ F |      | 8.1  | 13   | mA   |

| I <sub>VSD</sub>                       | Supply current, dc-mode                                        | $V_{VS}$ = 13.5V; $V_{EN}$ = HIGH; $V_{DIR}$ = LOW; S1 = S2 = GND $V_{PWM}$ = LOW; $C_{GHX}$ = 4.7nF $R_{PR}$ = 10k $\Omega$ ; $C_{PR}$ = 150pF                            |      | 5.8  | 10   | mA   |

| Enable in                              | put (EN)                                                       |                                                                                                                                                                            |      |      |      |      |

| V <sub>ENL</sub>                       | Low level                                                      |                                                                                                                                                                            |      |      | 1.5  | V    |

| V <sub>ENH</sub>                       | High level                                                     |                                                                                                                                                                            | 3.5  |      |      | V    |

| $V_{ENh}$                              | Hysteresis threshold <sup>2)</sup>                             |                                                                                                                                                                            |      | 1    |      | V    |

| R <sub>EN</sub>                        | Input pull down resistance                                     | V <sub>EN</sub> = 5V                                                                                                                                                       | 16   | 50   | 100  | kΩ   |

| H-bridge                               | control inputs (DIR, PWM)                                      | •                                                                                                                                                                          |      | •    | •    | •    |

| V <sub>DIRL</sub><br>V <sub>PWML</sub> | Input low level                                                |                                                                                                                                                                            |      |      | 1.5  | V    |

| V <sub>DIRH</sub><br>V <sub>PWMH</sub> | Input high level                                               |                                                                                                                                                                            | 3.5  |      |      | V    |

| $V_{DIRh}$ $V_{PWMh}$                  | Input threshold hysteresis <sup>2)</sup>                       |                                                                                                                                                                            |      | 1    |      | V    |

| R <sub>DIR</sub><br>R <sub>PWM</sub>   | Internal pull up resistance to internal VCC <sup>3)</sup>      | V <sub>DIR</sub> = 0; V <sub>PWM</sub> = 0                                                                                                                                 | 16   | 50   | 100  | kΩ   |

| DIAGNOS                                | STIC output (DG)                                               |                                                                                                                                                                            |      |      |      |      |

| $V_{DG}$                               | Output drop                                                    | I <sub>DG</sub> = 1mA                                                                                                                                                      |      |      | 0.6  | V    |

| $R_{DG}$                               | Internal pull up resistance to internal VCC <sup>3)</sup>      | V <sub>DG</sub> = 0V                                                                                                                                                       | 10   | 20   | 40   | kΩ   |

| Programi                               | mable cross conduction protectio                               | n <sup>4)</sup>                                                                                                                                                            |      |      |      |      |

| N <sub>PR</sub>                        | Threshold voltage ratio V <sub>PRH</sub> /<br>V <sub>PRL</sub> | $R_{PR} = 10k\Omega$                                                                                                                                                       | 1.8  | 2    | 2.2  |      |

| I <sub>PR</sub>                        | Current capability                                             | V <sub>PR</sub> = 2V                                                                                                                                                       | -0.5 |      |      | mA   |

| ISO inter                              | face, transmission input (TX)                                  | L                                                                                                                                                                          | 1    | L    | l    |      |

| V <sub>TXL</sub>                       | Input low level                                                |                                                                                                                                                                            |      |      | 1.5  | V    |

# Table 5. Electrical Characteristcs (continued)

(8V <  $V_{VS}$  < 20V,  $V_{EN}$  = HIGH, -40°C ≤  $T_{J}$  ≤ 150°C, unless otherwise specified. The voltages are refered to GND and currents are assumed positive, when current flows into the pin

| Symbol            | Parameter Test Condition                                  |                                                                  | Min.                      | Тур.                      | Max.            | Unit |

|-------------------|-----------------------------------------------------------|------------------------------------------------------------------|---------------------------|---------------------------|-----------------|------|

| V <sub>TXH</sub>  | Input high level                                          |                                                                  | 3.5                       |                           |                 | V    |

| V <sub>TXh</sub>  | Input hysteresis voltage 2)                               |                                                                  |                           | 1                         |                 | V    |

| R <sub>TX</sub>   | Internal pull up resistance to internal VCC 3)            | V <sub>TX</sub> = 0                                              | 10                        | 20                        | 40              | kΩ   |

| ISO inter         | face, receiver output (RX)                                | •                                                                |                           |                           |                 |      |

| V <sub>RXL</sub>  | Output voltage high stage                                 | TX = HIGH; I <sub>RX</sub> = 0; V <sub>K</sub> = V <sub>VS</sub> | 4.5                       |                           | 5.5             | V    |

| R <sub>RX</sub>   | Internal pull up resistance to internal VCC <sup>3)</sup> | TX = HIGH;<br>V <sub>RX</sub> = 0V                               | 5                         | 10                        | 20              | kΩ   |

| R <sub>RXON</sub> | ON resistance to ground                                   | TX = LOW;<br>I <sub>RX</sub> = 1mA                               |                           | 40                        | 90              | Ω    |

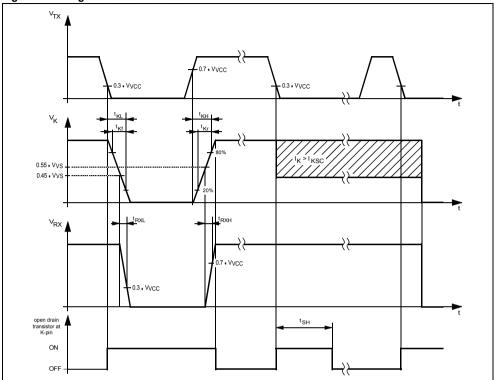

| t <sub>RXH</sub>  | Output high delay time                                    | Fig. 1                                                           |                           | 0.5                       |                 | μS   |

| t <sub>RXL</sub>  | Output low delay time                                     |                                                                  |                           | 0.5                       |                 | μS   |

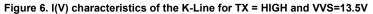

| ISO inter         | face, K-line (K)                                          |                                                                  |                           |                           |                 |      |

| $V_{KL}$          | Input low level                                           |                                                                  | -20V                      |                           | 0.45 ·<br>Vvs   |      |

| V <sub>KH</sub>   | Input high level                                          |                                                                  | 0.55 ·<br>V <sub>VS</sub> |                           | V <sub>VS</sub> |      |

| V <sub>Kh</sub>   | Input hysteresis voltage 2)                               |                                                                  |                           | 0.025·<br>V <sub>VS</sub> | 0.8V            |      |

| I <sub>KH</sub>   | Input current                                             | V <sub>TX</sub> = HIGH                                           | -5                        |                           | 25              | μА   |

| R <sub>KON</sub>  | ON resistance to ground                                   | V <sub>TX</sub> = LOW; I <sub>K</sub> =10mA                      |                           | 10                        | 30              | Ω    |

| Iksc              | Short circuit current                                     | V <sub>TX</sub> = LOW                                            | 40                        |                           | 130             | mA   |

| fĸ                | Transmission frequency                                    |                                                                  | 60                        | 100                       |                 | kHz  |

- 2. not tested in production: guaranteed by design and verified in characterization

- 3. Internal V<sub>VCC</sub> is 4.5V ... 5.5V

- 4. see page 18 for calculation of programmable cross conduction protection time

| t <sub>Kr</sub> | Rise time                    | Vvs = 13.5V; Fig. 1<br>External loads at K-line:<br>$R_K$ = 510 $\Omega$ pull up<br>to Vvs<br>$C_K$ = 2.2nF to GND |                                                                                 | 2 | 6                                                                               | μS |

|-----------------|------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---|---------------------------------------------------------------------------------|----|

| t <sub>Kf</sub> | Fall time                    |                                                                                                                    |                                                                                 | 2 | 6                                                                               | μS |

| t <sub>KH</sub> | Switch high delay time       |                                                                                                                    |                                                                                 | 4 | 17                                                                              | μS |

| t <sub>KL</sub> | Switch low delay time        |                                                                                                                    |                                                                                 | 4 | 17                                                                              | μS |

| tsн             | Short circuit detection time | V <sub>VS</sub> = 13.5V;<br>TX = LOW<br>V <sub>K</sub> > 0.55 · V <sub>VS</sub>                                    | 10                                                                              |   | 40                                                                              | μs |

| Charge p        | ump                          |                                                                                                                    |                                                                                 |   |                                                                                 |    |

| VCP             | Charge pump voltage          | $V_{VS} = 8V$ $V_{VS} = 13.5V$ $V_{VS} = 20V$                                                                      | V <sub>VS</sub> +<br>7V<br>V <sub>VS</sub> +<br>10V<br>V <sub>VS</sub> +<br>10V |   | V <sub>VS</sub> +<br>14V<br>V <sub>VS</sub> +<br>14V<br>V <sub>VS</sub><br>+14V |    |

Table 5. Electrical Characteristcs (continued)

(8V <  $V_{VS}$  < 20V,  $V_{EN}$  = HIGH, -40°C ≤  $T_{J}$  ≤ 150°C, unless otherwise specified. The voltages are referred to GND and currents are assumed positive, when current flows into the pin

| Symbol                                   | Parameter                                                             | Test Condition                                                                                                                             | Min.                     | Тур. | Max.                                      | Unit     |

|------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|-------------------------------------------|----------|

| I <sub>CP</sub>                          | Charging current<br>V <sub>CP</sub> = V <sub>VS</sub> + 8V            | V <sub>VS</sub> = 13.5V                                                                                                                    | -50                      | -75  |                                           | μА       |

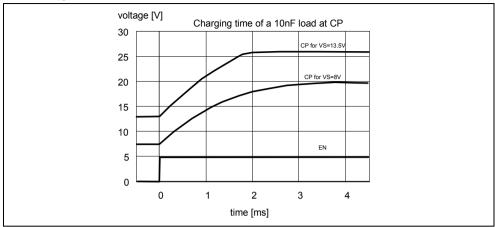

| t <sub>CP</sub>                          | Charging time <sup>2)</sup><br>V <sub>CP</sub> = V <sub>VS</sub> + 8V | V <sub>VS</sub> = 13.5V<br>C <sub>CP</sub> = 10nF                                                                                          |                          | 1.2  | 4                                         | ms       |

| f <sub>CP</sub>                          | Charge pump frequency                                                 | V <sub>VS</sub> = 13.5V                                                                                                                    | 250                      | 500  | 750                                       | kHz      |

| Drivers f                                | or external highside power MOS                                        |                                                                                                                                            |                          |      |                                           |          |

| V <sub>CB1</sub><br>V <sub>CB2</sub>     | Bootstrap voltage                                                     | $V_{VS} = 8V; \ I_{CBX} = 0; \ V_{SX} = 0$<br>$V_{VS} = 13.5V; \ I_{CBX} = 0; \ V_{SX} = 0$<br>$V_{VS} = 20V; \ I_{CBX} = 0; \ V_{SX} = 0$ | 7.5<br>10<br>10          |      | 14<br>14<br>14                            | > > >    |

| R <sub>GH1L</sub><br>R <sub>GH2L</sub>   | ON-resistance of SINK stage                                           | $V_{CBX} = 8V; V_{SX} = 0$<br>$I_{GHX} = 50mA; T_J = 25^{\circ}C$                                                                          |                          |      | 10                                        | Ω        |

|                                          |                                                                       | V <sub>CBX</sub> = 8V; V <sub>SX</sub> = 0<br>I <sub>GHX</sub> = 50mA; T <sub>J</sub> = 125°C                                              |                          |      | 20                                        | Ω        |

| R <sub>GH1H</sub><br>R <sub>GH2H</sub>   | ON-resistance of SOURCE stage                                         | I <sub>GHX</sub> = -50mA; T <sub>J</sub> = 25°C<br>I <sub>GHX</sub> = -50mA; T <sub>J</sub> = 125°C                                        |                          |      | 10<br>20                                  | $\Omega$ |

| V <sub>GH1H</sub><br>V <sub>GH2H</sub>   | Gate ON voltage (SOURCE)                                              | $V_{VS}$ = $V_{SX}$ = 8V; $I_{GHX}$ = 0; $C_{CBX}$ = 0.1 $\mu$ F                                                                           | V <sub>VS</sub><br>+6.5V |      | V <sub>VS</sub><br>+14V                   |          |

|                                          |                                                                       | $V_{VS} = V_{SX} = 13.5V; I_{GHX} = 0;$<br>$C_{CBX} = 0.1 \mu F$                                                                           | V <sub>VS</sub> +<br>10V |      | V <sub>VS</sub><br>+14V                   |          |

|                                          |                                                                       | $V_{VS} = V_{SX} = 20V; I_{GHX} = 0;$<br>$C_{CBX} = 0.1 \mu F$                                                                             | V <sub>VS</sub><br>+10V  |      | V <sub>VS</sub><br>+14V                   |          |

| R <sub>GH1</sub><br>R <sub>GH2</sub>     | Gate discharge resistance                                             | EN = LOW                                                                                                                                   | 10                       | 100  |                                           | kΩ       |

| R <sub>S1</sub><br>R <sub>S2</sub>       | Sink resistance                                                       |                                                                                                                                            | 10                       | 100  |                                           | kΩ       |

| Drivers f                                | or external lowside power MOS                                         | •                                                                                                                                          | •                        |      | •                                         | •        |

| R <sub>GL1L</sub><br>R <sub>GL2L</sub>   | ON-resistance of SINK stage                                           | I <sub>GLX</sub> = 50mA; T <sub>J</sub> = 25°C<br>I <sub>GLX</sub> = 50mA; T <sub>J</sub> = 125°C                                          |                          |      | 10<br>20                                  | $\Omega$ |

| R <sub>GL1H</sub> ,<br>R <sub>GL2H</sub> | ON-resistance of SOURCE stage                                         | $I_{GLX}$ = -50mA; $T_J$ = 25°C<br>$I_{GLX}$ = -50mA; $T_J$ = 125°C                                                                        |                          |      | 10<br>20                                  | Ω<br>Ω   |

| V <sub>GL1H</sub> ,<br>V <sub>GL2H</sub> | Gate ON voltage (SOURCE)                                              | $V_{VS} = 8V; I_{GLX} = 0$<br>$V_{VS} = 13.5V; I_{GLX} = 0$<br>$V_{VS} = 20V; I_{GLX} = 0$                                                 | 7V<br>10V<br>10V         |      | V <sub>VS</sub><br>V <sub>VS</sub><br>14V |          |

| R <sub>GL1</sub><br>R <sub>GL2</sub>     | Gate discharge resistance                                             | EN = LOW                                                                                                                                   | 10                       | 100  |                                           | kΩ       |

2. not tested in production: guaranteed by design and verified in characterization

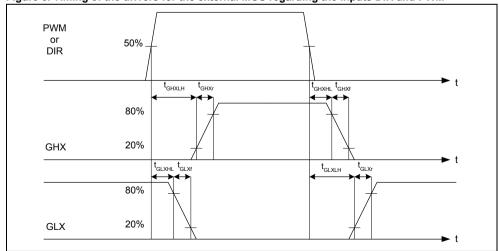

| Timing o         | Timing of the drivers  |                                                                                          |  |  |     |    |  |  |  |

|------------------|------------------------|------------------------------------------------------------------------------------------|--|--|-----|----|--|--|--|

| tgh1Lh<br>tgh2Lh | Propagation delay time | Fig. 2<br>$V_{VS} = 13.5V$<br>$V_{S1} = V_{S2} = 0$<br>$C_{CBX} = 0.1\mu F$<br>RPR= 10kW |  |  | 500 | ns |  |  |  |

47/

# Table 5. Electrical Characteristcs (continued)

(8V <  $V_{VS}$  < 20V,  $V_{EN}$  = HIGH, -40°C ≤  $T_{J}$  ≤ 150°C, unless otherwise specified. The voltages are refered to GND and currents are assumed positive, when current flows into the pin

| Symbol                                   | Parameter                                                                          | Test Condition                                                                                              | Min. | Тур. | Max. | Unit |

|------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------|------|------|------|

| t <sub>GH1LH</sub><br>t <sub>GH2LH</sub> | Propagation delay time including cross conduction protection time t <sub>CCP</sub> | Fig. 2<br>V <sub>VS</sub> = 13.5V<br>V <sub>S1</sub> = V <sub>S2</sub> = 0                                  | 0.7  | 1    | 1.3  | μS   |

| tgh1HL<br>tgh2HL                         | Propagation delay time                                                             | $C_{CBX} = 0.1 \mu F$ $C_{PR} = 150 p F;$ $R_{PR} = 10 k \Omega;$ 5)                                        |      |      | 500  | ns   |

| t <sub>GL1LH</sub><br>t <sub>GL2LH</sub> | Propagation delay time                                                             | Fig. 2<br>$V_{VS}$ = 13.5V<br>$V_{S1}$ = $V_{S2}$ = 0<br>$C_{CBX}$ = 0.1 $\mu$ F<br>$R_{PR}$ = 10k $\Omega$ |      |      | 500  | ns   |

| t <sub>GL1LH</sub><br>t <sub>GL2LH</sub> | Propagation delay time including cross conduction protection time tccp             | Fig. 2<br>Vvs = 13.5V<br>V <sub>S1</sub> = V <sub>S2</sub> = 0                                              | 0.7  | 1    | 1.3  | μS   |

| t <sub>GL1HL</sub><br>t <sub>GL2HL</sub> | Propagation delay time                                                             | $C_{CBX} = 0.1 \mu F$ $C_{PR} = 150 p F;$ $R_{PR} = 10 k \Omega;$ 5)                                        |      |      | 500  | ns   |

| t <sub>GH1r</sub><br>t <sub>GH2r</sub>   | Rise time                                                                          | Fig. 2<br>V <sub>VS</sub> = 13.5V                                                                           |      |      | 1    | μS   |

| t <sub>GH1f</sub><br>t <sub>GH2f</sub>   | Fall time                                                                          | $V_{S1} = V_{S2} = 0$<br>$C_{CBX} = 0.1 \mu F$                                                              |      |      | 1    | μS   |

| t <sub>GL1r</sub><br>t <sub>GL2r</sub>   | Rise time                                                                          | C <sub>GHX</sub> = 4.7nF<br>C <sub>GLX</sub> = 4.7nF                                                        |      |      | 1    | μS   |

| t <sub>GL1f</sub><br>t <sub>GL2f</sub>   | Fall time                                                                          | $R_{PR}$ = 10k $\Omega$ ;                                                                                   |      |      | 1    | μ\$  |

| Short Circ                               | cuit Detection                                                                     |                                                                                                             |      |      |      |      |

| V <sub>S1TH</sub><br>V <sub>S2TH</sub>   | Threshold voltage                                                                  |                                                                                                             |      | 4    |      | V    |

| t <sub>SCd</sub>                         | Detection time                                                                     |                                                                                                             | 5    | 10   | 15   | μS   |

| Step up c                                | onverter (ST) $(5.2V \le V_{VS} < 1)$                                              | 10V)                                                                                                        |      |      |      |      |

| V <sub>STH</sub>                         | ST disable HIGH threshold                                                          |                                                                                                             |      |      | 10   | V    |

| VsTh                                     | ST disable threshold hysteresis voltage <sup>2)</sup>                              |                                                                                                             | 1    |      | 2    | ٧    |

| R <sub>DSON</sub>                        | Open drain ON resistance                                                           | V <sub>VS</sub> = 5.2V;<br>I <sub>ST</sub> = 50mA                                                           |      |      | 20   | Ω    |

| f <sub>ST</sub>                          | Clock frequency                                                                    |                                                                                                             | 50   | 100  | 149  | kHz  |

|                                          |                                                                                    |                                                                                                             |      |      |      |      |

<sup>2.</sup> not tested in production: guaranteed by design and verified in characterization

<sup>5.</sup> tested with differed values in production but guaranteed by design and verified in characterization

Figure 4. Timing of the ISO-interface

Figure 5. Timing of the drivers for the external MOS regarding the inputs DIR and PWM

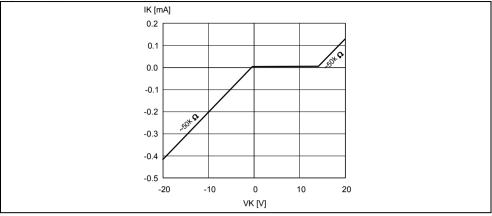

Figure 7. Driving sequence

Figure 8. Charging time of an external capacitor of 10nF connected to CP pin at  $\,V_{VS}$ =8V and  $\,V_{VS}$ =13.5V

Figure 9. Application Circuit Diagram

#### 3 FUNCTIONAL DESCRIPTION

#### 3.1 General

The L9904 integrated circuit (IC) is designed to control four external N-channel MOS transistors in H-Bridge configuration for DC-motor driving in automotive applications. It includes an ISO9141 compatible interface. A typical application is shown in fig.9.

#### 3.2 Voltage supply

The IC is supplied via an external reverse battery protection diode to the  $V_{VS}$  pin. The typical operating voltage range is down to 8V.

The supply current consumption of the IC composes of static and a dynamic part. The static current is typically 5.8mA. The dynamical current  $I_{dyn}$  is depending of the PWM frequency  $f_{PWM}$  and the required gate charge  $Q_{Gate}$  of the external power mos transistor. The current can be estimated by the expression:

$$I_{dyn} = 2 \cdot f_{PWM} \cdot Q_{Gate}$$

An external power transistor with a gate charge of  $Q_{Gate} = 160nC$  and a PWM frequency of  $f_{PWM} = 20kHz$  requires a dynamical supply current of  $I_{dyn} = 6.4mA$ .

The total supply current consumption is  $I_{VS} = 5.8 \text{mA} + 6.4 \text{mA} = 12.2 \text{mA}$ .

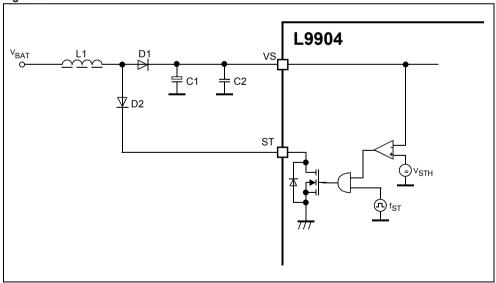

## 3.3 Extended supply voltage range (ST)

The operating battery voltage range can be extended down to 6V using the additional components shown in fig.7. A small inductor of L~150 $\mu$ H (I<sub>peak</sub>~500mA) in series to the battery supply builts up a step up converter with the switching open drain output ST. The switching frequency is typical 100kHz with a fixed duty cycle of 50%. The step up converter starts below V<sub>VS</sub> < 8V, increases the supply voltage at the V<sub>S</sub> pin and switches off at V<sub>VS</sub> > 10V to avoid EME at nominal battery voltage. The diode D2 in series with the ST pin is necessary only for systems with negative battery voltage. No additional load can be driven by the step up converter.

Figure 10.

#### 3.4 Control inputs (EN, DIR, PWM)

The cmos level inputs drive the device as shown in fig.7 and described in the truth table.

The device is activated with enable input HIGH signal. For enable input floating (not connected) or VEN=0V the device is in standby mode. When activating the device a wake-up time of 50µs is recommended to stabilize the internal supplies.

The DIR and PWM inputs control the driver of the external H-Bridge transistors. The motor direction can be choosen with the DIR input, the duty cycle and frequency with the PWM input. Unconnected inputs are defined by internal pull up resistors. During wake-up and braking and before disactivating the IC via enable both inputs should be driven HIGH.

Table 6. Truth table:

| Status | Cor | Control inputs |     |    | Device status |    | Driver stage for external power MOS |                 |                 | ternal          | Diagnostic     | Comment |                     |

|--------|-----|----------------|-----|----|---------------|----|-------------------------------------|-----------------|-----------------|-----------------|----------------|---------|---------------------|

|        | EN  | DIR            | PWM | TS | OV            | UV | sc                                  | GH1             | GL1             | GH2             | GL2            | DG      |                     |

| 1      | 0   | х              | х   | Х  | Х             | х  | Х                                   | R <sup>7)</sup> | R               | R <sup>7)</sup> | R              | Т       | standby mode        |

| 2      | 1   | х              | х   | 1  | 0             | 0  | 0                                   | L               | L               | L               | L              | L       | thermal<br>shutdown |

| 3      | 1   | х              | х   | 0  | 1             | 0  | 0                                   | L               | L               | L               | L              | L       | overvoltage         |

| 4      | 1   | х              | х   | 0  | 0             | 1  | 0                                   | L               | L               | L               | L              | L       | undervoltage        |

| 5      | 1   | х              | х   | 0  | 0             | 0  | 1                                   | X <sup>6)</sup> | X <sup>6)</sup> | X <sup>6)</sup> | X <sup>6</sup> | L       | short circuit 6)    |

| 6      | 1   | 0              | 0   | 0  | 0             | 0  | 0                                   | L               | Н               | Н               | L              | Н       |                     |

| 7      | 1   | х              | 1   | 0  | 0             | 0  | 0                                   | L               | Н               | L               | Н              | Н       | braking mode        |

| 8      | 1   | 1              | 0   | 0  | 0             | 0  | 0                                   | Н               | L               | L               | Н              | Н       |                     |

Symbols: x Don't care

R:Resistive output

TS:Thermal shutdown OV:Overvoltage

0: Logic LOW or not active1: Logic HIGH or active

L: Output in sink conditionH: Output in source condition

UV:Undervoltage

T: Tristate

SC:Short Circuit

## 3.5 Thermal shutdown

When the junction temperature exceeds  $T_{JSD}$  all driver are switched in sink condition (L), the K- output is off and the diagnostic DG is LOW until the junction temperature drops below  $T_{JSD}$  -  $T_{JHYST}$ .

## 3.6 Overvoltage Shutdown

When the supply voltage  $V_{VS}$  exceeds the overvoltage threshold  $V_{VSOVH}$  all driver are switched in sink condition (L), the K- output is off and the diagnostic DG is LOW.

#### 3.7 Undervoltage Shutdown

For supply voltages below the undervoltage disable threshold the gate driver remains in sink condition (L) and the diagnostic DG is low.

Only those external MOS transistors of the H-Bridge which are in short circuit condition are switched off. All others remain driven by DIR and PWM.

<sup>7.</sup> See Application Note AN2229

#### 3.8 Short Circuit Detection

The output voltage at the S1 and S2 pin of the H-Bridge is monitored by comparators to detect shorts to ground or battery. The activated external highside MOS transistor will be switched off if the voltage drop remains below the comparator threshold voltage  $V_{\rm S1TH}$  and  $V_{\rm S2TH}$  for longer than the short current detection time  $t_{\rm SCd}$ . The transistor remains in off condition, the diagnostic output goes LOW until the DIR or PWM input status will be changed. The status doesn't change for the other MOS transistors. The external lowside MOS transistor will be switched off if the voltage drop passes over the comparator threshold voltage  $V_{\rm S1TH}$  and  $V_{\rm S2TH}$  for longer than the short current detection time  $t_{\rm SCd}$ . The transistor remains in off condition, the diagnostic output goes LOW until the DIR or PWM input status will be changed. The status doesn't change for the other MOS transistors.

#### 3.9 Diagnostic Output (DG)

The diagnostic output provides a real time error detection, if monitors the following error stacks: Thermal shutdown, overvoltage shutdown, undervoltage shutdown and short circuit shutdown. The open drain output with internal pull up resistor is LOW if an error is occuring.

#### 3.10 Bootstrap capacitor (CB1,CB2)

To ensure, that the external power MOS transistors reach the required  $R_{DSON}$ , a minimum gate source voltage of 5V for logic level and 10V for standard power MOS transistors has to be guaranteed. The highside transistors require a gate voltage higher than the supply voltage. This is achieved with the internal chargepump circuit in combination with the bootstrap capacitor. The bootstrap capacitor is charged, when the highside MOS transistor is OFF and the lowside is ON. When the lowside is switched OFF, the charged bootstrap capacitor is able to supply the gate driver of the highside power MOS transistor. For effective charging the values of the bootstrap capacitors should be larger than the gate-source capacitance of the power MOS and respect the required PWM ratio

#### 3.11 Chargepump circuit (CP)

The reverse battery protection can be obtained with an external N-channel MOS transistor as shown in fig.6. In this case its drain-bulk diode provides the protection. The output CP is intended to drive the gate of this transistor above the battery voltage to switch on the MOS and to bypass the drain-bulk diode with the  $R_{DSON}$ . The CP has a connection to VS through an internal diode and a  $20k\Omega$  resistor.

#### 3.12 Gate drivers for the external N-channel power MOS transistors (GH1, GH2, GL1, GL2)

High level at EN activates the driver of the external MOS under control of the DIR and PWM inputs (see truth table and driving sequence fig.4). The external power MOS gates are connected via series resistors to the device to reduce electro magnetic emission (EME) of the system. The resistors influence the switching behaviour. They have to be choosen carefully. Too large resistors enlarge the charging and discharging time of the power MOS gate and can generate cross current in the halfbridges. The driver assures a longer switching delay time from source to sink stage in order to prevent the cross conduction.

The gate source voltage is limited to 14V. The charge/discharge current is limited by the R<sub>DSON</sub> of the driver. The drivers are not protected against shorts.

## 3.13 Programmable cross conduction protection

The external power MOS transistors in H-Bridge ( two half bridges) configuration are switched on with an additional delay time  $t_{\rm CCP}$  to prevent cross conduction in the halfbridge. The cross conduction protection time  $t_{\rm CCP}$  is determined by the external capacitor  $C_{\rm PR}$  and resistor  $R_{\rm PR}$  at the PR pin. The capacitor  $C_{\rm PR}$  is charged up to the voltage limit  $V_{\rm PRH}$ . A level change on the control inputs DIR and PWM switches off the concerned external MOS transistor and the charging source at the PR pin. The resistor  $R_{\rm PR}$  discharges the capacitor  $R_{\rm PR}$  reaches the value of  $R_{\rm PR}$  After that the CPR will be charged again. The capacitor  $R_{\rm PR}$  should be choosen between 100pF and 1nF. The resistor  $R_{\rm PR}$  should be higher than 7kW. The delay time can be expressed as follows:

$t_{CCP} = R_{PR} \cdot C_{PR} \cdot In N_{PR}$  with  $N_{PR} = V_{PRH} / V_{PRL} = 2$

tccp= 0.69 · Rpr · Cpr

#### 3.14 ISO-Interface

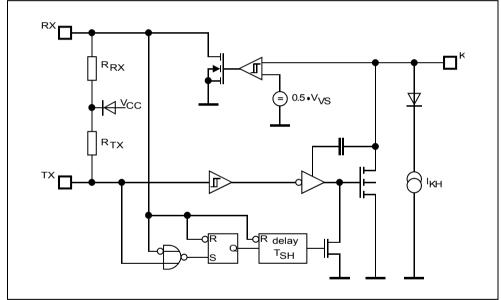

The ISO-Interface provides the communication between the micro controller and a serial bus with a baud rate up to 60kbit/s via a single wire which is  $V_{BAT}$  and GND compatible. The logic level transmission input TX drives the open drain K-output. The K output can be connected to a serial bus with a pull up resistor to  $V_{BAT}$ . The K-pin is protected against overvoltage, short to GND and VS and can be driven beyond  $V_{VS}$  and GND. During lack of  $V_{VS}$  or GND the output shows high impedance characteristic. The open drain output RX with an internal pull up resistor monitors the status at the K-pin to read the received data and control the transmitted data. Short circuit condition at K-pin is recognized if the internal open drain transistor isn't able to pull the voltage potential at K-pin below the threshold of  $0.45 \cdot V_{VS}$ . Then the RX stays in high condition. A timer starts and switches the open drain transistor after typ. 20µs off. A next low at the TX input resets the timer and the open drain transistor switches on again.

Figure 11. Functional schematic of the ISO-interface

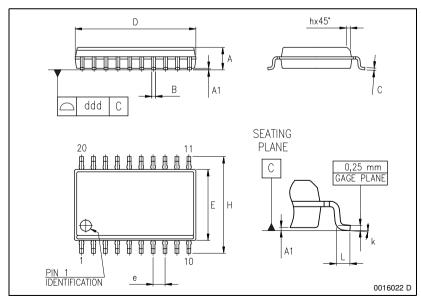

Figure 12. SO20 Mechanical Data & Package Dimensions

| DIM.             |       | mm   |           |         |       |       |

|------------------|-------|------|-----------|---------|-------|-------|

| Diwi.            | MIN.  | TYP. | MAX.      | MIN.    | TYP.  | MAX.  |

| Α                | 2.35  |      | 2.65      | 0.093   |       | 0.104 |

| A1               | 0.10  |      | 0.30      | 0.004   |       | 0.012 |

| В                | 0.33  |      | 0.51      | 0.013   |       | 0.200 |

| С                | 0.23  |      | 0.32      | 0.009   |       | 0.013 |

| D <sup>(1)</sup> | 12.60 |      | 13.00     | 0.496   |       | 0.512 |

| Е                | 7.40  |      | 7.60      | 0.291   |       | 0.299 |

| е                |       | 1.27 |           |         | 0.050 |       |

| Н                | 10.0  |      | 10.65     | 0.394   |       | 0.419 |

| h                | 0.25  |      | 0.75      | 0.010   |       | 0.030 |

| L                | 0.40  |      | 1.27      | 0.016   |       | 0.050 |

| k                |       | 0    | * (min.), | 8° (max | .)    |       |

| ddd              |       |      | 0.10      |         |       | 0.004 |

<sup>(1) &</sup>quot;D" dimension does not include mold flash, protusions or gate burrs. Mold flash, protusions or gate burrs shall not exceed 0.15mm per side.

# OUTLINE AND MECHANICAL DATA

# Table 7. Revision History

| Date           | Revision | Description of Changes                         |

|----------------|----------|------------------------------------------------|

| October 2002   | 1        | First Issue on ST-Press DMS                    |

| January 2004   | 2        | Migration from ST-Press to EDOCS DMS           |

| May 2004       | 3        | Change Maturity from Product Preview to Final. |

| October 2005   | 4        | Inserted on pag 12 AN2229 ref.                 |

| September 2013 | 5        | Updated disclaimer.                            |

# Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

DocID9019 Rev 5 17/17